Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

Notícia

Página inicial > Notícia > Unidade servo de alta velocidade com base em CPLD e codificador absoluto

2024-04-01

Atualmente, os servo motores em máquinas -ferramentas domésticas CNC geralmente são equipadas com codificadores incrementais, enquanto a precisão dos codificadores incrementais não é muito alta e a saída é de sinais paralelos. Para melhorar sua precisão, é necessário aumentar o projeto do codificador. Dificuldade e aumentar a produção de sinais paralelos, o que não é propício à comunicação de longa distância entre a unidade servo e o codificador. O codificador absoluto é usado, exceto que sua precisão é várias vezes maior que a do codificador incremental. A comunicação serial de alta velocidade salva linhas de comunicação para comunicação de longa distância. Na outra extremidade do codificador, o CPLD e o codificador absoluto são usados para comunicação serial de alta velocidade. O CPLD converte as informações do codificador recebido em transmissão de dados paralelos. O DSP na unidade servo executa controle aritmético. Este artigo fornecerá o design de software e hardware da comunicação serial de alta velocidade entre CPLD e Codificador Absoluto .

Design de hardware

O hardware é composto principalmente por três módulos: fonte de alimentação, CPLD e seus circuitos periféricos e circuito de interface do codificador absoluto.

Módulo de potência

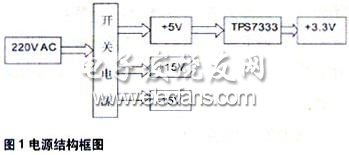

O módulo de energia consiste em um circuito de fonte de alimentação de comutação e um chip de fonte de alimentação DC/DC, como mostrado na Figura 1.

A fonte de alimentação de comutação na figura converte a tensão da grade CA de 220V em +5V, +15V, -15V. A fonte de alimentação de comutação pode filtrar várias interferências na rede elétrica, e o transformador na fonte de alimentação de comutação será de 220V e a saída é + 5V, + 15V, -15V é isolada, o circuito interno também usa TL431 para ajustar o Largura do pulso de condução do tubo de comutador, portanto, a regulação anti-interferência, segurança, estabilidade e tensão da fonte de alimentação de comutação é melhor. O TPS7333 é um chip DC/DC. A tensão de +5V CC é convertida em uma tensão CC estável de +3,3V para uso pelo CPLD. O TPS7333 possui uma melhor eficiência de conversão, confiabilidade e regulação de tensão. Pode ser usado na faixa de tensão de +3,77V- +10V. A conversão +3,3V faz com que o CPLD seja queimado devido à tensão de entrada muito alta.

CPLD e seus módulos de circuito periférico

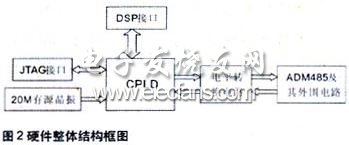

O CPLD e seus módulos de circuito periférico são compostos principalmente por CPLD, CPLD Programming Download Interface Circuit (interface JTAG), circuito de interface DSP, oscilador de cristal ativo, circuito de conversão de nível e ADM485 e seus circuitos periféricos (circuito de interface responsável pela comunicação com o codificador) . Figura 2).

Este CPLD de design usa o EPM570T144C5 da Altera, que pertence ao Max II de Altera. O Max II é menor em custo que o máximo I e consome menos energia. O dispositivo possui mais células macro e o atraso do dispositivo é controlado dentro de 6 ns. Com desempenho de alto custo, o EPM570T144C5 possui 570 macrocélulas. O número de pinos no chip é 144, dos quais 116 estão disponíveis portas de E/S, portanto os recursos desse chip são suficientes. O CPLD é principalmente responsável pela comunicação serial de alta velocidade com o codificador absoluto e é controlado pelo comando DSP para encaminhar os dados do codificador e outras informações ao DSP em paralelo.

A interface JTAG é usada principalmente para baixar o arquivo executável no CPLD, instalar o ambiente de desenvolvimento da empresa Altera - Quartus II no PC e compilar o programa VHDL escrito nesse ambiente de desenvolvimento para garantir que a compilação não seja livre de erros e a função é implementada. Conecte o cabo de download à interface JTAG e faça o download da placa CPLD através da ferramenta de download de programação fornecida pelo Quartus II.

A interface DSP consiste em 8 linhas de dados, 3 linhas de endereço e 1 linha de controle. As 8 linhas de dados são responsáveis por transferir os dados do codificador e outras informações. As três linhas de endereço são responsáveis por transmitir comandos DSP e decodificar no terminal CPLD. O CPLD transmite os dados do codificador ou outras informações para o DSP através de 8 linhas de dados de acordo com o comando decodificado. A linha de controle completa principalmente o controle síncrono da CPLD e do DSP.

O oscilador de cristal ativo de 20m fornece principalmente um relógio de referência para o CPLD. Sob a direção do sinal do relógio, o CPLD gera uma taxa de transmissão de 2,5 MB/s para se comunicar com o codificador e gera um relógio de 10m Hz para alguns sinais de controle lógico. Fornecer uma frequência de relógio de 20m Hz requer uma tensão de 3,3V DC da fonte de alimentação.

O circuito de mudança de nível é principalmente responsável pela conversão de 3.3V a 5V ou 5V a 3,3V, porque as portas do núcleo e E/S do CPLD requerem uma tensão de alimentação de 3,3V, necessária para ADM485 e codificadores absolutos. A tensão de alimentação e o circuito do driver de porta de E/S são 5V, por isso é necessário converter 3.3V a 5V ou 5V a 3,3V com o nível de conversão de conversão LVC4245A.

ADM485 e seus circuitos periféricos são a conexão de hardware entre a CPLD e a comunicação absoluta de alta velocidade do codificador. A tensão de trabalho do ADM485 é 5V e sua velocidade máxima de comunicação é de 5 MB/s. O uso de dois chips ADM485 para encaixar a comunicação pode melhorar a capacidade anti-interferência na linha de comunicação, e a distância de transmissão mais longa pode atingir 1,2 km. O circuito periférico é mostrado na Figura 3. A metade direita da linha pontilhada pertence ao circuito periférico do codificador absoluto. Os resistores de pull-up e pull-down são 1K ohms, o resistor limitador atual é de 220 ohms e o SDAT ADM485 é o pino de saída de dados. ADM485 é SRQ é o pino de entrada de dados, DE OF ADM485 é o pino de controle externo, este pino é controlado pela CPLD. Como o protocolo de comunicação RS-485 é meio-duplex, o ADM485 só pode estar no estado de enviar dados ou receber dados. Quando o ADM485 é de alta, o ADM485 está no estado de saída de dados (ou seja, o CPLD recebe dados). Quando o DE do ADM485 é de baixo nível, o ADM485 está no estado de entrada de dados (ou seja, o CPLD envia dados).

Compartilhar no:

Enviar Inquérito

Ms. carol Dong

Número De Telefone:86-431-85543703

Fax:86-431---88634119

Celular:+8613894866263

E-mail:sales@encoders.com.cn

Endereço:333Feiyue Donglu, Changchun City, Jilin Province. China, Changchun, Jilin

Site móvel

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

Fill in more information so that we can get in touch with you faster

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.